- 您现在的位置:买卖IC网 > Sheet目录1918 > DSPIC33FJ32MC202-E/MM (Microchip Technology)IC DSPIC MCU/DSP 32K 28QFN

dsPIC33FJ32MC202/204 and dsPIC33FJ16MC304

DS70283K-page 18

2007-2012 Microchip Technology Inc.

3.3

Special MCU Features

The dsPIC33FJ32MC202/204 and dsPIC33FJ16MC304

features a 17-bit by 17-bit single-cycle multiplier that is

shared by both the MCU ALU and DSP engine. The

multiplier can perform signed, unsigned and mixed-sign

multiplication. Using a 17-bit by 17-bit multiplier for 16-bit

by 16-bit multiplication not only allows you to perform

mixed-sign multiplication, it also achieves accurate results

for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJ32MC202/204 and dsPIC33FJ16MC304

supports 16/16 and 32/16 divide operations, both

fractional and integer. All divide instructions are iterative

operations. They must be executed within a REPEAT loop,

resulting in a total execution time of 19 instruction cycles.

The divide operation can be interrupted during any of

those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit

left or right shift in a single cycle. The barrel shifter can

be used by both MCU and DSP instructions.

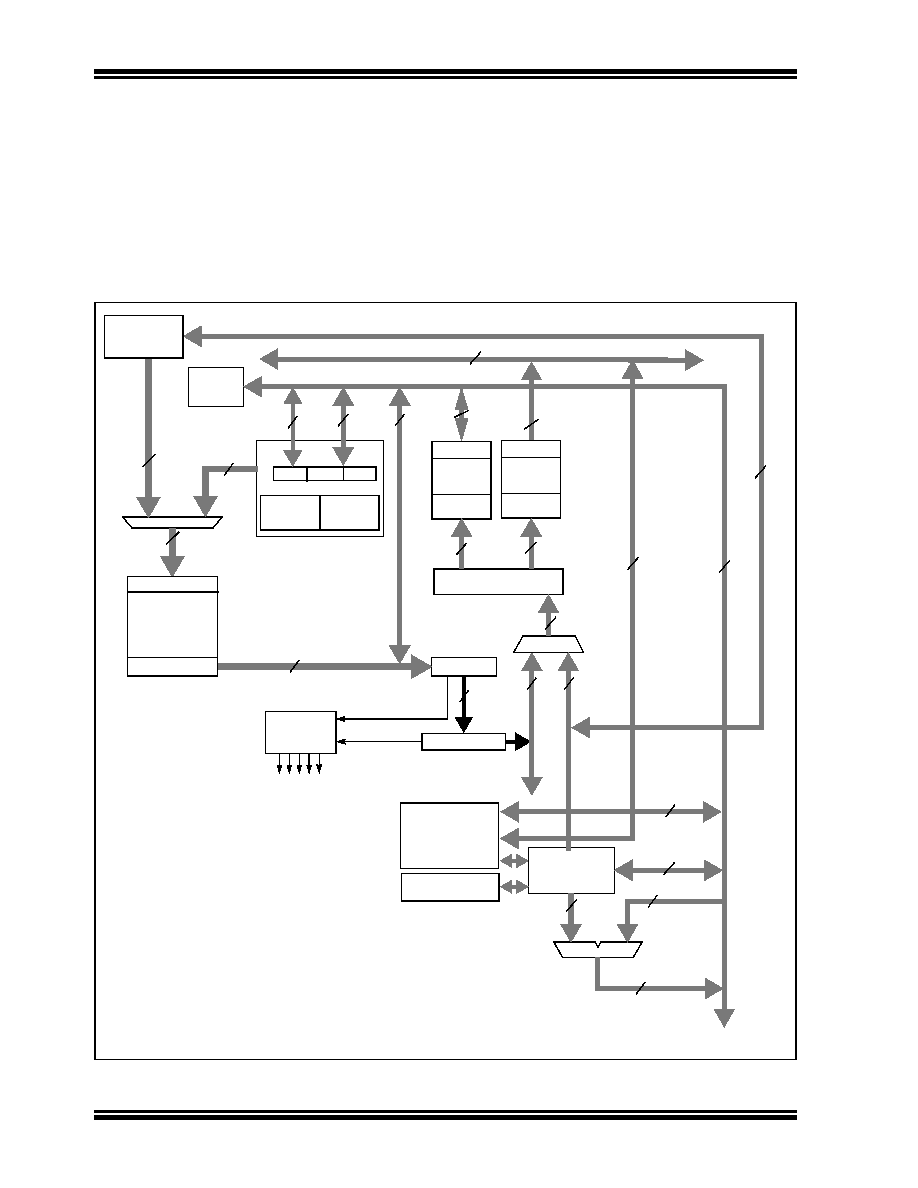

FIGURE 3-1:

dsPIC33FJ32MC202/204 and dsPIC33FJ16MC304 CPU CORE BLOCK DIAGRAM

Instruction

Decode and

Control

PCH

PCL

Program Counter

16-bit ALU

24

23

Instruction Reg

PCU

16 x 16

W Register Array

ROM Latch

EA MUX

Interrupt

Controller

Stack

Control

Logic

Loop

Control

Logic

Data Latch

Address

Latch

Control Signals

to Various Blocks

L

ite

ra

lD

at

a

16

To Peripheral Modules

Data Latch

Address

Latch

16

X RAM

Y RAM

Address Generator Units

16

Y Data Bus

X Data Bus

DSP Engine

Divide Support

16

23

16

8

PSV and Table

Data Access

Control Block

16

Program Memory

Data Latch

Address Latch

16

24

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC33FJ64MC710-I/PF

IC DSPIC MCU/DSP 64K 100TQFP

EFM32G200F64

MCU 32BIT 64KB FLASH 32-QFN

EFM32G210F128

IC MCU 32BIT 128KB FLASH 32QFN

EFM32G222F64

IC MCU 32BIT 64KB FLASH QFP48

EFM32G230F128

IC MCU 32BIT 128KB FLASH 64QFN

EFM32G232F64

IC MCU 32BIT 64KB FLASH LQFP64

EFM32G280F64

MCU 32BIT 64KB FLASH 100-LQFP

EFM32G290F64

MCU 32BIT 64KB FLASH 112-BGA

相关代理商/技术参数

dsPIC33FJ32MC202-E/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 16B DSC 28LD32KB Motor40 MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC33FJ32MC202-E/SP

功能描述:数字信号处理器和控制器 - DSP, DSC 16B DSC 28LD32KB Motor40 MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC33FJ32MC202-E/SS

功能描述:数字信号处理器和控制器 - DSP, DSC 16 bit DSC 40MIPS 32KB Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC33FJ32MC202-H/MM

功能描述:数字信号处理器和控制器 - DSP, DSC 16-bit 32KB Flash 40 MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC33FJ32MC202-H/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 16-bit 32KB Flash 40 MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC33FJ32MC202-I/MM

功能描述:数字信号处理器和控制器 - DSP, DSC 16B DSC 28LD 32KB FlashMotor40 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC33FJ32MC202-I/MM

制造商:Microchip Technology Inc 功能描述:16 bit DSC 28LD 32KB Flash Motor 40 MIPS

DSPIC33FJ32MC202-I/MM

制造商:Microchip Technology Inc 功能描述:DSC 16BIT 32K FLASH 40MIPS 28QFN-S 制造商:Microchip Technology Inc 功能描述:DSC, 16BIT, 32K FLASH, 40MIPS, 28QFN-S